-

-

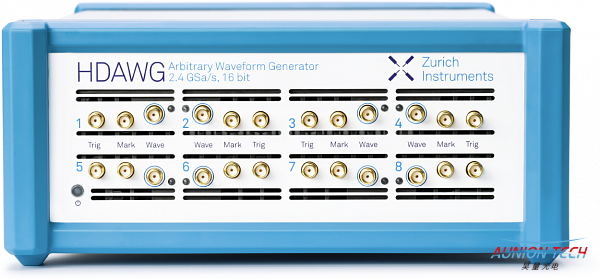

瑞士苏黎世仪器 多通道任意波形发生器HDAWG

- 品牌:瑞士苏黎世仪器

- 型号: HDAWG

- 产地:瑞士

- 供应商报价: 面议

-

上海昊量光电设备有限公司

更新时间:2024-04-17 15:27:18

更新时间:2024-04-17 15:27:18 -

企业性质授权代理商

入驻年限第4年

营业执照已审核

- 同类产品信号发生器(10件)

联系方式:贺先生156-01689581

联系我们时请说明在仪器网(www.yiqi.com)上看到的!

-

为您推荐

- 瑞士苏黎世仪器 多通道任意波形发生器HDAWG 核心参数

- 详细介绍

多通道任意波形发生器

苏黎世仪器HDAWG多通道任意波形发生器AWG在这一级别产品中通道密度相对高,带宽高达750MHz。HDAWG多通道任意波形发生器有4 / 8个直流耦合,16bit垂直分辨率的单端模拟输出通道。 输出可以在一个直接模式中单独切换,具有优越的噪声性能,和一个放大模式将信号振幅提高到zui大值5 Vpp。在保证16位输出分辨率的同时,保证每通道2个标记设置同步。.

LabOne®软件基于先进的编程理念,它结合了AWG的性能和灵活性和函数发生器器的易用性。独立于平台的LabOne用户界面(UI)和虚拟仪器改编LabVIEW,NET,MATLAB,C,和Python支持简单测量自动化和快速集成到现有的控制环境。

HDAWG关键特性

2.4 GSa/s, 16 bit, 750 MHz信号带宽

5 Vpp zui大振幅

可扩展到64路输出通道

高通道密度

Trigger输出延迟低于50ns

多频数字调制

LabOne® AWG定序器和编序器

HDAWG应用

量子计算

激光雷达

核磁共振光谱

半导体测试

MIMO技术

HDAWG多通道任意波形发生器一款高端仪器,通过扩展核心AWG功能来满足苛刻的应用程序的要求:附加波形存储器,函数发生器功能,内部振荡器,一组脉冲计数器。

量子计算和相控阵雷达

多个HDAWG仪器可以自动同步和控制使用单一的用户界面,使雷达和量子计算系统的有效扩展,同时减少复杂性和实验室所需的空间。50纳秒反应时间短到外部触发信号使量子纠错和高保真度的方法。内部振荡器小化波形上传时间,确保相位相干性,并提供一个更简单的波形的定义。综合脉冲计数器帮助简化设置捕获离子和N-Vzhong心实验。

核磁共振和光谱

MR和其他光谱学应用的信号发生在从纳秒到秒的时间尺度上。HDAWG可以通过应用变量采样率和/或参数扫描来加速这些测量。使用数字调制,可以在一个或多个载波信号上施加一个任意的包络,并且在不需要额外的努力的情况下保持相位一致。

半导体测试

嵌套排序、波形迭代和动态序列控制是实现大规模高通量测试信号的理想选择。将AWG信号与函数发生器信号相乘或添加,可以扩展可能性,帮助简化和加速日常的测量程序。

HDAWG亮点集锦

高水平AWG编程

LabOne UI的设计目的是通过提供一种直观的、易读的形式来快速地提供硬件控制。在LabOne AWG音序器中定义了波形和序列之后,LabOne AWG编译器将指令转换成机器语言,并在很短的时间内将结果传输到硬件。LabOne测序支持动态变化的延迟和条件分支点的循环。

除了标准波形外,如高斯、布莱克曼、sin函数等,LabOne包含复杂波形设计所需的所有必要的数学和阵列编辑工具。您可以轻松地添加、复制、剪切和连接波形或将它们组织成段。从另一个工具(如MATLAB)中计算出的测量信号或波形是一个简单的拖放操作。

多设备同步

多台HDAWGs可以作为单一的多通道AWG进行操作:

l 所有仪器使用一个UI/API

l 所有输出通道同步

l 所有仪器时钟相位锁定

l UHF系列仪器的同步时间标记和采样率

当使用多个仪器时,LabOne AWG编译器负责将您的主序列程序分布到所有的工具中。自动触发交换协议确保同步播放时间。使用MDS,你还可以建立一个完整的信号生成和采集系统,包括UHF仪器,包括600MHz锁相放大器,boxcar, digitizer和AWG功能。

振荡器,调制,相位控制

HDAWG配备了数字振荡器,可以独立于程控的AWG包络信号产生信号的正弦载波。这意味着可以通过快的波形上传和许多脉冲的相位相干来生成长信号。将会被写入静态波形的载波频率和相位可以自由调整和扫掠。HDAWG-MF多频选项增加了振荡器的数量,使频率和相位调制、频率多路复用或相位循环实现全数字I/Q调制。在HDAWG-FG函数发生器选项中,调制概念扩展到正弦载波以外的一般载波波形。

低延迟触发和序列分支

由于低延迟的设计,HDAWG能够在信号输出小于50 ns的情况下产生它的di一个样本,而在前面板上的一个触发器输入中检测到一个外部触发器。这对于量子计算的反馈实验至关重要,因为在量子计算中,设备的性能是短暂的,而每一纳秒的保存都极大地提高了实验结果。仪器的4或8个输出通道可分为2或4个单元。每一组都可以单独触发,在将信号分配到devic的各个部分时增加灵活性。

HDAWG 规格

Arbitrary Waveform Generator

channels

4 (HDAWG4 model)

8 (HDAWG8 model)vertical resolution

16 bit

waveform memory per channel

64 MSa;

500 MSa (with HDAWG-ME option)sequence memory

16384 instructions

waveform granularity

8 samples

minimum waveform length

32 samples

sequencer clock frequency

sampling rate divided by 8

sequencer instructions (playback)

play waveform (single or multi-channel),

play waveform segment (start sample index and segment length),

play waveform from the library (DIO input state), interrupt waveform playbacksequencer instructions (other)

wait constant, wait for trigger, set/get trigger state, set/get DIO state,

integer variable operations (add, subtract, logical operations),

change oscillator frequency/phase (real-time), change other

instrument setting (non real-time)sequencer control structures

repeat (1 to 223-1 or infinite), conditional branch (multi-branch)

Wave Output

connector type

SMA

output impedance

50 Ω

output coupling

DC

output modes

amplified, direct

output range (into 50 Ω)

0.2 to 5.0 Vpp (amplified)

0.8 Vpp (direct)offset voltage (into 50 Ω)

0.5 × peak voltage, max. ±1.25 V (amplified)

0 V (direct)phase noise

<−110 dBc/Hz (100 MHz, offset 10 kHz)

voltage noise

above 200 kHz30 nV/√Hz (amplified, 5 Vpp range)

12 nV/√Hz (direct)Time & Frequency Domain Characteristics

frequency range, max. amplitude

into 50 Ω0 − 300 MHz, 5.0 Vpp

0 − 750 MHz, 0.8 Vppsampling clock source

internal, external

sampling rate

1.5 kSa/s to 2.4 GSa/s (internal clock)

50 MSa/s to 2.4 GSa/s (external clock)internal sampling clock resolution

7 digits

rise time (20% to 80%)

< 550 ps (amplified, 1 V step, 5 Vpp output range)

< 300 ps (direct, 0.8 V step)trigger delay to output

< 50 ns

skew between channels

< 200 ps (any two channels)

< 20 ps (channels 1&2, 3&4, ...)skew adjustment range

10 ns

skew adjustment resolution

10 ps

Marker & Other Outputs

marker outputs

2 per channel, 1 SMA output per channel on front panel,

additional outputs on DIO on back panelsampling clock output

SMA on back panel

sampling clock output amplitude

2 Vpp

reference clock output

SMA on back panel

reference clock output amplitude

1 Vpp

reference clock output frequency

10 / 100 MHz

Inputs

trigger inputs

1 per channel, SMA on front panel

trigger input impedance

50 Ω / 1 kΩ

trigger input amplitude range

±5 V (50 Ω)

±10 V (1 kΩ)trigger input threshold range

±5 V (50 Ω)

±10 V (1 kΩ)trigger input threshold resolution

< 0.4 mV

sampling clock input

SMA on back panel

reference clock input

SMA on back panel

reference clock input frequency

10 / 100 MHz

Maximum Ratings

damage threshold

Sampling Clock input±5 V

damage threshold Ref input

±5 V

Connectivity & Others

digital IO (DIO)

VHDCI 68 pin female connector,

32 bit, configurable as input or output, 3.3 V TTLhost connection

LAN / Ethernet, 1 Gbit/s

USB 3.0, 5 Gbit/sPC memory requirements

4 GB+

PC CPU requirements

Compatibility with SSE2 instruction set required.

Examples: AMD K8 (Athlon 64, Sempron 64, Turion 64, etc.),

AMD Phenom, Intel Pentium 4, Xeon, Celeron, Celeron D,

Pentium M, Celeron M, Core, Core 2, Core i5, Core i7, Core i3, Atomoperating system

See LabOne Compatibility

General

dimensions

43.0 × 23.2 × 10.2 cm

16.9 × 9.2 × 4.0 inch, suited for 19 inch rackweight

4.6 kg; 10.2 lbs

power supply AC line

100-240 V (±10%), 50/60 Hz

operating temperature

+5 °C to +40 °C

operating environment

IEC61010, indoor location, installation category II, pollution degree 2

operating altitude

up to 2000 meters

| 输出波形: | 正弦 | 信号频率: | 低频 |